## scheda integrativa 13A 1

## Studio analitico del funzionamento on-off del BJT

Usare un transistor in funzionamento on-off vuole dire farlo funzionare in saturazione (on) e in interdizione (off).

### Saturazione

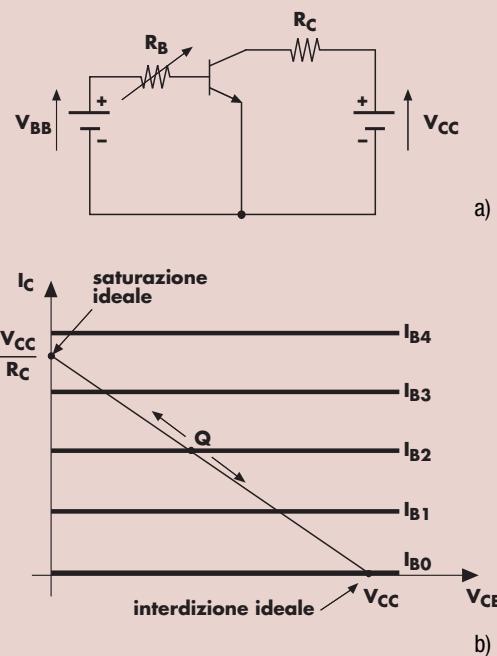

Si consideri la **figura 1** dove si prende in esame un BJT, espresso tramite le sue curve idealizzate, polarizzato con un circuito dove è prevista la possibilità di variare il valore di  $R_B$  e quindi, tramite essa, la corrente di base.

**Figura 1** Studio idealizzato del funzionamento on-off.

Si immagini che inizialmente il transistor sia polarizzato in modo da presentare un punto di funzionamento statico **Q** in zona attiva: se ora si aumenta  $I_B$  attraverso la riduzione di  $R_B$ , il punto **Q** si sposta verso l'alto lungo la retta di carico statica, avvicinandosi al punto di saturazione ideale. Il tutto è conseguenza del fatto che si è ipotizzato:

$$I_C = h_{FE} I_B \quad (1)$$

Se si continua ad aumentare  $I_B$  fino a raggiungere il punto di saturazione ideale, dove il BJT si comporta da cortocircuito, un ulteriore aumento della corrente di base non può comportare un corrispondente aumento di  $I_C$  e quindi, detta  $I_{CMAX}$  la massima corrente di collettore possibile nel circuito, che nel nostro particolare caso risulta:

$$I_{CMAX} = \frac{V_{CC}}{R_C} \quad (2)$$

se il BJT è saturo risulta:

$$h_{FE} I_B \geq I_{CMAX} \quad \text{ovvero} \quad I_B \geq \frac{I_{CMAX}}{h_{FE}} \quad (3)$$

La (3) è quindi la condizione che idealmente garantisce la saturazione del BJT.

In realtà la saturazione reale si discosta sempre da quella ideale a causa della c.d.t.  $V_{CE}$  che non è mai nulla. In pratica, un BJT è saturo se presenta una c.d.t. residua tra collettore ed emettitore  $V_{CESAT} = 0,2 \div 0,4$  V (fino a 1 V per transistor di potenza che operano con correnti elevate).

Per garantire la saturazione nella realtà, è poi opportuno tenere presente che  $h_{FE}$  non è un parametro effettivamente costante, ma che è dipendente dalla temperatura e dal valore di  $I_C$  e che, inoltre, il suo valore è dichiarato con ampie tolleranze costruttive.

Per tenere conto di questi ulteriori fattori conviene assegnare ad  $h_{FE}$  il valore minimo prevedibile, in relazione ai dati dichiarati dal costruttore. In altri termini si può dire che la condizione (3) che garantisce la saturazione va così modificata:

$$I_B \geq \frac{I_{CMAX}}{h_{FEmin}} \quad (4)$$

In questo modo la saturazione è garantita per qualsiasi valore di  $h_{FE}$  possibile: se le tolleranze costruttive portano a un valore di  $h_{FE}$  più grande del valore minimo, la diseguaglianza è, a maggior ragione, comunque verificata.

Va, infine, osservato che, oltre al BJT, anche gli altri componenti circuituali (resistenze e tensione di alimentazione) possono presentare delle tolleranze e quindi, per essere sicuri che la saturazione si verifichi effettivamente, è necessario assegnare a  $I_B$  un valore superiore al minimo necessario imposto dalla (4). Siccome però una corrente di base eccessiva, oltre che determinare una inutile dissipazione termica, causa tempi di commutazione tra saturazione e interdizione troppo elevati, non conviene aumentare più di tanto il valore di  $I_B$  minimo necessario, ottenuto dalla (4). Mediamente si può ritenerne corretto un valore di  $I_B$  aumentato del 20%. Ovvero, per ottenere con certezza la saturazione di un BJT si può assegnare a  $I_B$  un valore  $I_{Bsat}$ :

$$I_{Bsat} = 1,2 \frac{I_{CMAX}}{h_{FEmin}} \quad (5)$$

Il successivo esempio dovrebbe chiarire il tutto. Va peraltro osservato che la (5) è una formula pratica non vincolante, ma comunque atta a garantire la saturazione.

**Esempio 1**

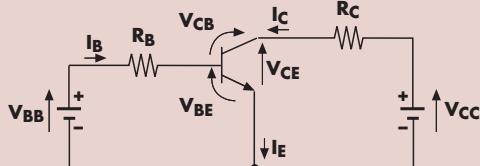

Posto, nel circuito di figura,  $V_{CC} = V_{BB} = 15$  V, dimensionare le resistenze per ottenere la saturazione del BJT con una corrente di collettore di 100 mA, sapendo che il transistor scelto (per esempio BC368) per questa corrente presenta un  $h_{FEmin} = 70$  e una  $V_{CEsat} = 0,4$  V.

**Figura 2** Circuito dell'esempio 1.

Si può iniziare dimensionando  $R_C$  applicando Kirchhoff alla maglia di uscita:

$$V_{CC} = R_C I_C + V_{CEsat} \Rightarrow R_C = \frac{V_{CC} - V_{CEsat}}{I_C} = \frac{15 - 0,4}{100 \cdot 10^{-3}} = 146 \Omega$$

Facendo riferimento alla serie commerciale E24 si può usare un resistore da 150  $\Omega$ .

Per la (5) la corrente di base che garantisce la saturazione è:

$$I_{Bsat} = 1,2 \frac{I_{CMAX}}{h_{FEmin}} = 1,2 \frac{100 \cdot 10^{-3}}{70} \approx 1,7 \text{ mA}$$

Applicando Kirchhoff alla maglia di ingresso si dimensiona  $R_B$ :

$$V_{BB} = R_B I_{Bsat} + V_{BE} \Rightarrow R_B = \frac{V_{BB} - V_{BE}}{I_{Bsat}} = \frac{15 - 0,7}{1,7 \cdot 10^{-3}} \approx 8,4 \text{ k}\Omega$$

Si usa il valore commerciale di 8,2 k $\Omega$  (serie E24).

**Esempio 2**

Facendo ancora riferimento alla **figura 2**, sapendo che:

$$V_{CC} = V_{BB} = 12 \text{ V}; h_{FE} = 100; V_{CEsat} = 0,4 \text{ V}; \\ V_{BE} = 0,7 \text{ V}; R_C = 1 \text{ k}\Omega; R_B = 47 \text{ k}\Omega$$

verificare che il BJT è saturo.

La  $I_{CMAX}$  risulta:

$$I_{CMAX} = \frac{V_{CC} - V_{CEsat}}{R_C} = \frac{12 - 0,4}{1000} = 11,6 \text{ mA}$$

La  $I_B$  risulta:

$$I_B = \frac{V_{BB} - V_{BE}}{R_B} \approx 240 \mu\text{A} > \frac{I_{CMAX}}{h_{FE}} = 116 \mu\text{A}$$

e quindi il BJT è saturo.

**Interdizione**

Ritornando alla **figura 1**, se ora si immagina di aumentare sempre più il valore di  $R_B$ , il punto di funzionamento **Q** si sposterà verso il basso, avvicinandosi al punto di interdizione ideale che verrà raggiunto con una  $I_B = I_{B0} = 0$ .

Si potrebbe quindi pensare che la piena interdizione del transistor, che corrisponde al funzionamento del transistor tra collettore ed emettitore come un circuito aperto, si ottenga ponendo  $I_B = 0$  ovvero aprendo la maglia di ingresso ( $R_B = \infty$ ). In realtà in corrispondenza di  $I_{B0} = 0$  la  $I_E$  non è nulla, sebbene molto piccola, ma è presente una corrente residua che scorre tra collettore ed emettitore, indicata con la sigla  $I_{CEO}$  (corrente tra collettore ed emettitore con la base aperta).

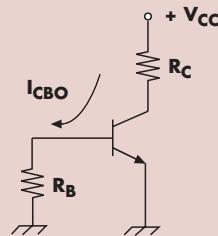

Questa corrente, che è comunque molto piccola (al massimo pochi  $\mu\text{A}$  nei transistor al Si), permette, ai fini pratici, di ritenere interdetto il transistor quando si annulla la corrente di base. Se però si vuole la piena interdizione, annullando completamente la corrente tra collettore ed emettitore, si deve effettuare il collegamento indicato in **figura 3**.

**Figura 3** Circuito per la piena interdizione di un BJT al Si.

In questo circuito si è supposto di spostare il terminale di  $R_B$  che si trovava a  $+V_{BB}$  portandolo a massa: in queste condizioni si produce una debole corrente tra collettore e base mentre si annulla la corrente  $I_E$ . Si può quindi effettivamente dire che il transistor è interdetto, e si tenga anche presente che  $I_{CBO}$  (corrente tra collettore e base con l'emettitore aperto) è una corrente molto piccola (minore della  $I_{CEO}$ ) e si verifica con la giunzione base-collettore polarizzata inversamente (vedere anche il paragrafo 5).