scheda integrativa **4B** (2)**Simbologia nei circuiti digitali**

Attualmente i simboli logici usati non seguono una standardizzazione precisa e questo spesso può creare confusione: le abitudini simbolistiche attualmente più diffuse si rifanno comunque in buona parte alle norme MIL Std. 806B. L'esigenza di una effettiva standardizzazione ha fatto sì che alcuni comitati tecnici (IEC: *International Electrotechnical Commission*; IEEE: *Institute of Electrical and Electronics Engineers*; ANSI: *American National Standard Institute*) abbiano sviluppato diverse proposte che hanno portato a un nuovo standard simbolistico ANSI/IEEE Std. 91-1984 che si sta abbastanza diffondendo e che compare anche in diversi data sheet riportati nel manuale dei data sheet.

Si fornisce in questa scheda una sintesi di queste nuove norme e un confronto con quelle attualmente più usate.

Le caratteristiche della simbologia MIL possono essere sintetizzate nei cinque punti seguenti.

1) Per le porte logiche si usano i simboli riportati in **figura 1**.

| Porta logica | Norme |           |

|--------------|-------|-----------|

|              | MIL   | ANSI/IEEE |

| AND          |       |           |

| OR           |       |           |

| NOT          |       |           |

| NAND         |       |           |

| NOR          |       |           |

| XOR          |       |           |

| XNOR         |       |           |

**Figura 1** Simboli logici.

- 2) Gli IC MSI e LSI vengono rappresentati con un rettangolo senza alcuna suddivisione interna.

3) Un cerchietto indica negazione e quindi, se posto davanti a un ingresso o dopo un'uscita, indica che si tratta, in logica positiva, di un ingresso o di un'uscita attiva bassa (sarebbe il contrario in logica negativa); in altri termini l'assenza del cerchietto indica che è attivo l'1, la sua presenza che è attivo lo 0.

4) All'interno di un rettangolo le sigle letterali non sono mai negate; all'esterno, prima o dopo un cerchietto, sì.

5) Gli ingressi attivi su un fronte vengono indicati con un triangolino interno al rettangolo dell'integrato.

Le norme ANSI/IEEE possono essere sintetizzate nei nove punti seguenti.

1) Ogni funzione logica, sia che si tratti di una porta che di un integrato complesso, viene rappresentata con un rettangolo.

2) I simboli delle porte sono riportati in **figura 1**.

3) Per gli IC MSI e LSI il rettangolo viene diviso internamente per evidenziare le parti logiche che lo compongono.

4) Eventuali ingressi che agiscono su tutto l'integrato vengono fatti confluire in un blocco a forma di *T*, posto nella parte superiore del rettangolo principale.

5) Gli ingressi sono sulla sinistra e le uscite sulla destra del rettangolo.

6) Gli ingressi attivi bassi sono indicati con un triangolino (*indicatore di polarità*) posto esternamente al rettangolo, e analogamente si procede per le uscite; l'orientamento del triangolino indica il flusso dati.

7) La singola funzione logica è evidenziata da un apposito *simbolo qualificatore* posto vicino al lato superiore del rettangolo; in **tavella 1** sono riportati i principali simboli qualificatori (per un elenco completo si rinvia alla letteratura tecnica relativa a queste norme).

|                  |                                        |

|------------------|----------------------------------------|

| <b>&amp;</b>     | funzione AND                           |

| <b>= 1</b>       | funzione OR esclusivo                  |

| <b>1</b>         | uscita attivata da un solo ingresso    |

| <b>MUX</b>       | multiplexer                            |

| <b>Σ</b>         | addizionatore                          |

| <b>P-Q</b>       | sottrattore                            |

| <b>Σ</b>         | monostabile                            |

| <b>CTRm</b>      | contatore a m bit                      |

| <b>≥1</b>        | funzione OR                            |

| <b>=</b>         | identità logica                        |

| <b>X/Y</b>       | decodificatore, convertitore di codice |

| <b>DMUX o DX</b> | demultiplexer                          |

| <b>π</b>         | moltiplicatore                         |

| <b>COMP</b>      | comparatore                            |

| <b>Σ</b>         | astabile                               |

| <b>CTR DIVm</b>  | contatore modulo m                     |

**Tavella 1** Siglatura logica secondo le norme ANSI/IEEE.

8) Gli ingressi attivi su un fronte sono indicati con un triangolino interno al rettangolo.

9) Le eventuali correlazioni esistenti tra più terminali vengono evidenziate tramite delle *notazioni di dipendenza* (vedi **tavella 2**; per un elenco completo vedere i data sheet); per indicare le dipendenze

si assegna un numero a ogni termine influenzato e quello influenzante viene indicato con una lettera che evidenzia il tipo di dipendenza, seguita dai numeri dei terminali dipendenti.

|                    |                           |

|--------------------|---------------------------|

| <b>A</b> indirizzo | <b>R</b> reset            |

| <b>C</b> controllo | <b>S</b> set              |

| <b>N</b> negazione | <b>Z</b> interconnessione |

| <b>G</b> AND       | <b>EN</b> abilitazione    |

| <b>M</b> modo      |                           |

| <b>V</b> OR        |                           |

**Tabella 2** Notazioni di dipendenza.

La **figura 2** riporta le convenzioni più significative tra gli ingressi e le uscite secondo le norme ANSI/IEEE.

**Figura 2** Convenzioni ingressi e uscite.

### Un esempio

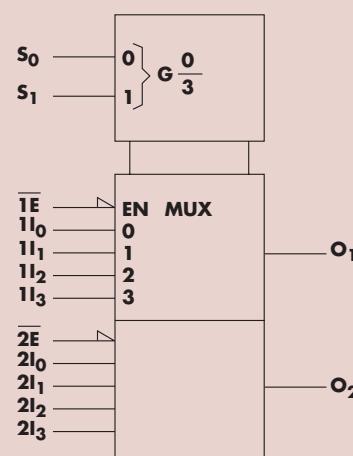

La **figura 3** riporta il simbolo secondo le norme ANSI/IEEE del 54/74153 (*Manuale dei data sheet*, parte 4): come si vede, si tratta di un doppio multiplexer con gli ingressi di selezione in comune, come chiarito dal fatto che questi ingressi confluiscono nel blocco a T. Questi ingressi di selezione sono legati da un'operazione di AND con gli ingressi di segnale 0, 1, 2, 3 dei due multiplexer, come indicato dalla notazione di dipendenza G0/3. Gli ingressi di enable (notazione di dipendenza EN) sono attivi bassi.

### Alcune osservazioni

Nei simboli delle porte logiche le scritte interne hanno la funzione di chiarire il comportamento logico.

Così, in particolare, nell'OR la scritta  $\leq 1$  indica che l'uscita è attiva se almeno un ingresso è attivo, nell'EX-OR la scritta  $=1$  indica che l'uscita è attiva se solo un ingresso è attivo, nel NOT l'1 indica che se l'unico ingresso è attivo (ovvero a livello alto) allora l'uscita è attiva (cioè a livello basso).

Nei simboli MIL gli ingressi sono intesi attivi in termini logici, ovvero l'assenza del cerchiolino indica che l'ingresso (o l'uscita) è attivo con l'1 e la presenza del cerchiolino che è attivo con lo 0.

Nei simboli ANSI/IEEE gli ingressi sono intesi attivi in termini elettrici, infatti l'assenza dell'indicatore di polarità indica che l'ingresso (o l'uscita) è attivo alto e viceversa è attivo basso.

Usando le norme MIL per associare lo 0 e l'1 ai livelli logici e quindi descrivere il comportamento di una funzione logica in termini elettrici (ovvero in termini di livelli alti o bassi) bisogna chiarire se si opera in logica positiva o negativa; così ad esempio in logica positiva un NAND ha gli ingressi attivi alti e l'uscita attiva bassa.

Usando le norme ANSI/IEEE non è necessario chiarire la logica che si considera (positiva o negativa) per descrivere il comportamento elettrico di una funzione logica; infatti, ad esempio, un NAND va inteso come un dispositivo con gli ingressi attivi alti che, se sono entrambi attivi, portano l'uscita al livello attivo (basso); ovviamente, in termini di 0 e 1, se si opera in logica positiva il dispositivo è ancora un NAND mentre in logica negativa è un NOR.

Queste norme permettono una più completa informazione sul funzionamento del singolo dispositivo, ma la loro minore intuibilità e le abitudini radicate dei progettisti ne limitano lo sviluppo.

**Figura 3** Simboli ANSI/IEEE del '54/74153.