scheda integrativa **4B** 3

## **Circuiti rilevatori d'errori**

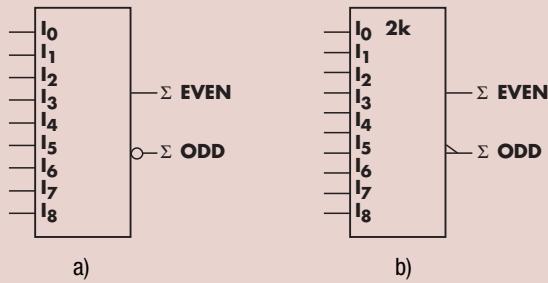

Un esempio di IC commerciale generatore/rilevatore di parità è il 54/74280 (anche LS-S-HC); in **figura 1** ne è riportato il simbolo logico (anche secondo le norme ANSI/IEEE) e in **tavella 1** è riportata la sua tabella della verità. Si vede che presenta nove ingressi e due uscite, una attiva alta ( $\Sigma$  EVEN) che va a livello alto (ovvero a 1 in logica positiva) se il numero di 1 in ingresso è pari, e una attiva bassa ( $\Sigma$  ODD) che nelle stesse condizioni va bassa (ovvero a 0 in logica positiva).

**Figura 1** Simbolo logico del '280 (a) e simbolo secondo le norme ANSI/IEEE (b).

| Numero di 1 (H)<br>in ingresso | Uscite        |              |

|--------------------------------|---------------|--------------|

|                                | $\Sigma$ EVEN | $\Sigma$ ODD |

| 0 - 2 - 4 - 6 - 8              | H             | L            |

| 1 - 3 - 5 - 7 - 9              | L             | H            |

**Tabella 1** Tabella della verità del '280.

Se questo IC viene usato come rilevatore di parità, usando l'uscita  $\Sigma$  EVEN si dice che opera con *even high parity* (parità pari a livello alto); operando sempre con parità pari a livello alto, e rinunciando a uno degli ingressi da porre a livello basso, l'uscita  $\Sigma$  ODD genera il bit di parità.

È anche possibile usare questo IC con *odd high parity* (parità dispari a livello alto, ovvero disparità a livello alto) invertendo il ruolo delle due uscite. Si potrebbe anche pensare di operare non sulla parità o disparità degli 1 ma degli 0 (*even low parity* e *odd low parity*).

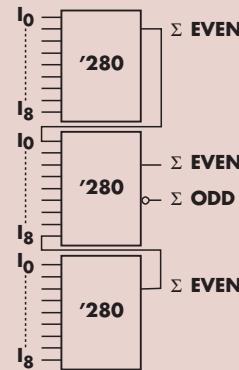

**Figura 2** Esempio di generatore/rilevatore di parità a 25 linee.

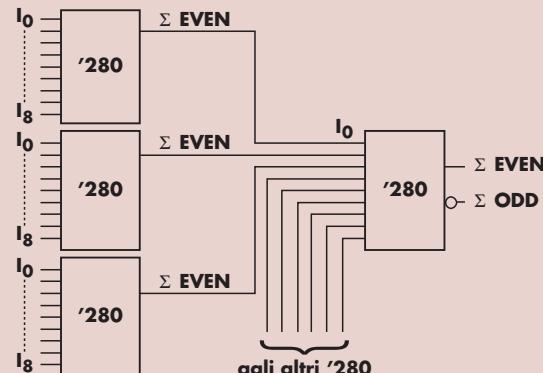

Le **figure 2** e **3** riportano due possibili modalità d'uso di questo IC con più di 9 linee dati. Per ulteriori notizie si rinvia ai data sheet e alle *application note* dei costruttori.

**Figura 3** Esempio di generatore/rilevatore di parità a 81 linee.